# Robustness

Rick Kazman

Phil Bianco

Sebastián Echeverría

James Ivers

**March 2022**

**TECHNICAL REPORT**

CMU/SEI-2022-TR-004

DOI: 10.1184/R1/16455660

**Software Solutions Division**

[Distribution Statement A] Approved for public release and unlimited distribution

<http://www.sei.cmu.edu>

Copyright 2021 Carnegie Mellon University.

This material is based upon work funded and supported by the Department of Defense under Contract No. FA8702-15-D-0002 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center.

The view, opinions, and/or findings contained in this material are those of the author(s) and should not be construed as an official Government position, policy, or decision, unless designated by other documentation.

References herein to any specific commercial product, process, or service by trade name, trade mark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by Carnegie Mellon University or its Software Engineering Institute.

This report was prepared for the SEI Administrative Agent AFLCMC/AZS 5 Eglin Street Hanscom AFB, MA 01731-2100

NO WARRANTY. THIS CARNEGIE MELLON UNIVERSITY AND SOFTWARE ENGINEERING INSTITUTE MATERIAL IS FURNISHED ON AN "AS-IS" BASIS. CARNEGIE MELLON UNIVERSITY MAKES NO WARRANTIES OF ANY KIND, EITHER EXPRESSED OR IMPLIED, AS TO ANY MATTER INCLUDING, BUT NOT LIMITED TO, WARRANTY OF FITNESS FOR PURPOSE OR MERCHANTABILITY, EXCLUSIVITY, OR RESULTS OBTAINED FROM USE OF THE MATERIAL. CARNEGIE MELLON UNIVERSITY DOES NOT MAKE ANY WARRANTY OF ANY KIND WITH RESPECT TO FREEDOM FROM PATENT, TRADEMARK, OR COPYRIGHT INFRINGEMENT.

[DISTRIBUTION STATEMENT A] This material has been approved for public release and unlimited distribution. Please see Copyright notice for non-US Government use and distribution.

Internal use: \* Permission to reproduce this material and to prepare derivative works from this material for internal use is granted, provided the copyright and "No Warranty" statements are included with all reproductions and derivative works.

External use: \* This material may be reproduced in its entirety, without modification, and freely distributed in written or electronic form without requesting formal permission. Permission is required for any other external and/or commercial use. Requests for permission should be directed to the Software Engineering Institute at [permission@sei.cmu.edu](mailto:permission@sei.cmu.edu).

\* These restrictions do not apply to U.S. government entities.

Architecture Tradeoff Analysis Method® and ATAM® are registered in the U.S. Patent and Trademark Office by Carnegie Mellon University.

DM21-0920

---

## Table of Contents

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>Abstract</b>                                                    | <b>v</b>  |

| <b>1 Goals of This Document</b>                                    | <b>1</b>  |

| <b>2 On Robustness</b>                                             | <b>3</b>  |

| <b>3 Evaluating the Robustness of an Architecture</b>              | <b>6</b>  |

| 3.1 Measuring Robustness                                           | 6         |

| 3.2 Reasoning About Robustness Properties                          | 8         |

| 3.3 Operationalizing the Measurement of Robustness                 | 9         |

| <b>4 Robustness Scenarios</b>                                      | <b>10</b> |

| 4.1 General Scenario for Robustness                                | 11        |

| 4.2 Example Scenarios for Robustness                               | 12        |

| 4.2.1 Scenario 1: System Initialization Times Out                  | 14        |

| 4.2.2 Scenario 2: Software Fault and Recovery                      | 14        |

| 4.2.3 Scenario 3: Resource Threshold Is Approached                 | 15        |

| 4.2.4 Scenario 4: Hardware Failure and Restart                     | 15        |

| <b>5 Mechanisms for Achieving Robustness</b>                       | <b>16</b> |

| 5.1 Tactics                                                        | 16        |

| 5.1.1 Detect Faults                                                | 19        |

| 5.1.2 Recover from Faults                                          | 21        |

| 5.1.3 Prevent Faults                                               | 24        |

| 5.2 Patterns                                                       | 26        |

| 5.2.1 Process Pairs                                                | 26        |

| 5.2.2 Triple Modular Redundancy                                    | 27        |

| 5.2.3 N+1 Redundancy                                               | 27        |

| 5.2.4 Circuit Breaker                                              | 28        |

| 5.2.5 Recovery Blocks                                              | 28        |

| 5.2.6 Forward Error Recovery                                       | 29        |

| 5.2.7 Health Monitoring                                            | 30        |

| 5.2.8 Throttling                                                   | 30        |

| <b>6 Analyzing for Robustness</b>                                  | <b>31</b> |

| 6.1 Tactics-Based Questionnaire                                    | 31        |

| 6.2 Architecture Analysis Checklist for Robustness                 | 36        |

| 6.3 Robustness Models and Analysis Techniques                      | 38        |

| 6.3.1 Non-state Based Modeling Techniques                          | 42        |

| 6.3.2 State-Based Modeling Techniques                              | 47        |

| 6.3.3 Sample Tool Support for Robustness Modeling                  | 58        |

| <b>7 Playbook for an Architecture Analysis of Robustness</b>       | <b>60</b> |

| 7.1 Step 1—Collect Artifacts                                       | 60        |

| 7.2 Step 2—Identify the Mechanisms Used to Satisfy the Requirement | 61        |

| 7.3 Step 3—Locate the Mechanisms in the Architecture               | 63        |

| 7.4 Step 4—Identify Derived Decisions and Special Cases            | 64        |

| 7.5 Step 5—Assess Requirement Satisfaction                         | 66        |

| 7.6 Step 6—Assess Impact on Other Quality Attribute Requirements   | 67        |

| 7.7 Step 7—Assess the Costs/Benefits of the Architecture Approach  | 69        |

|          |                        |           |

|----------|------------------------|-----------|

| <b>8</b> | <b>Summary</b>         | <b>71</b> |

| <b>9</b> | <b>Further Reading</b> | <b>72</b> |

|          | <b>Bibliography</b>    | <b>73</b> |

---

## List of Figures

|                                                                                                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1: The Form of a General Scenario                                                                                            | 11 |

| Figure 2: Robustness Tactics                                                                                                        | 17 |

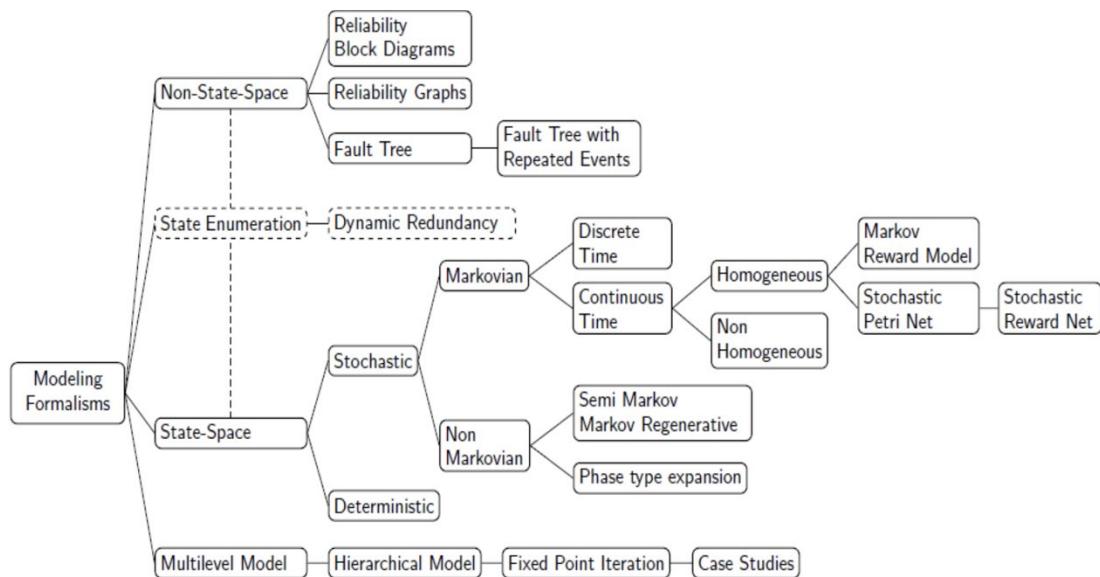

| Figure 3: Reliability Modeling Formalisms [Source: Trivedi 2017, Figure 2.6, p. 28]                                                 | 39 |

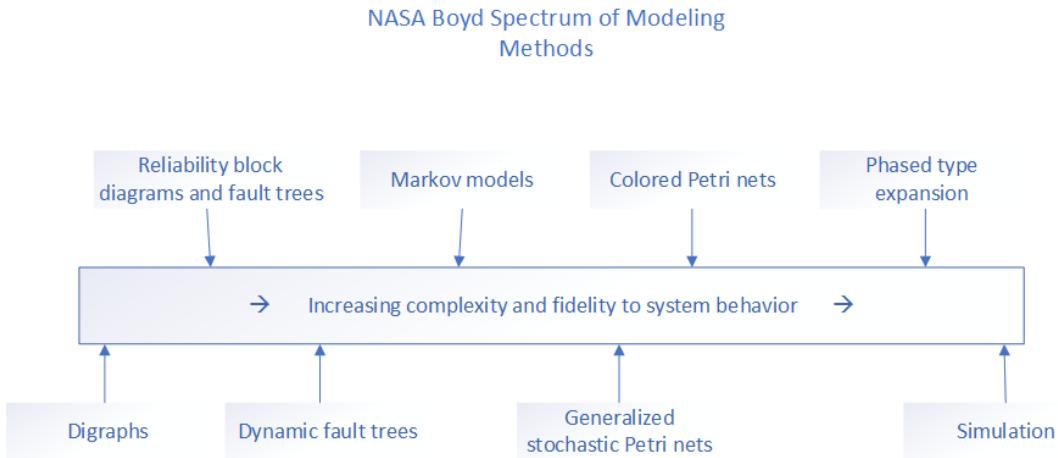

| Figure 4: A Spectrum of Modeling Methods [Derived from Boyd 1998]                                                                   | 41 |

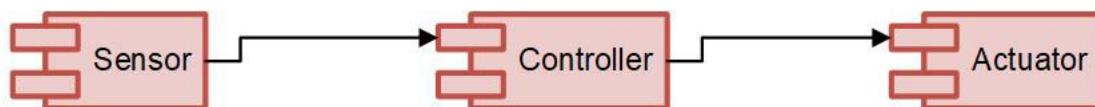

| Figure 5: A Simple Series RBD Diagram                                                                                               | 42 |

| Figure 6: A Group of Sensors (Employing an Active Redundancy Tactic) to Improve Robustness                                          | 42 |

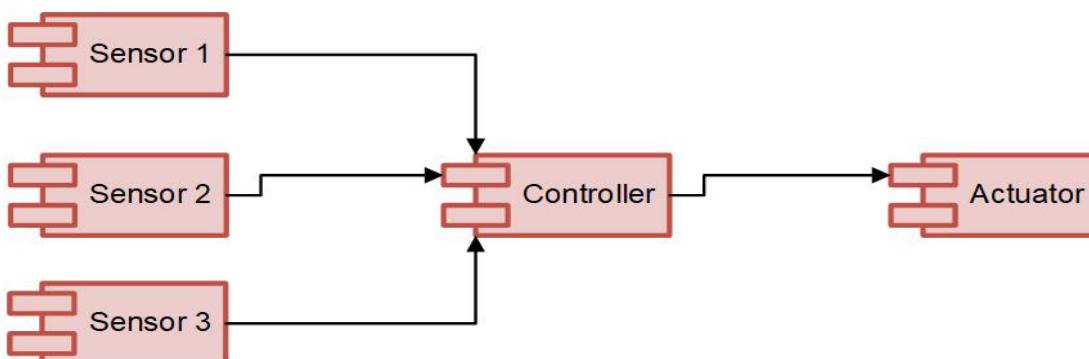

| Figure 7: Number of Parallel Components [Derived from Cepin 2011]                                                                   | 43 |

| Figure 8: Equivalent Fault Tree of Simple Series RBD Diagram                                                                        | 44 |

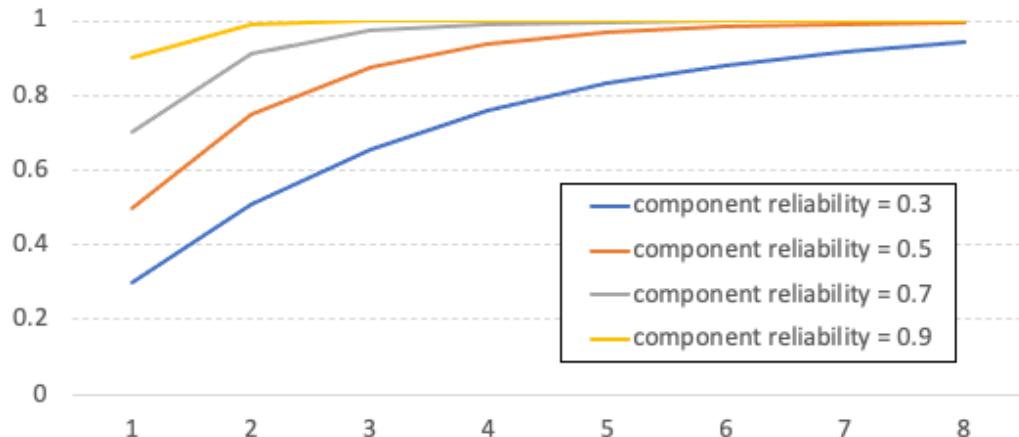

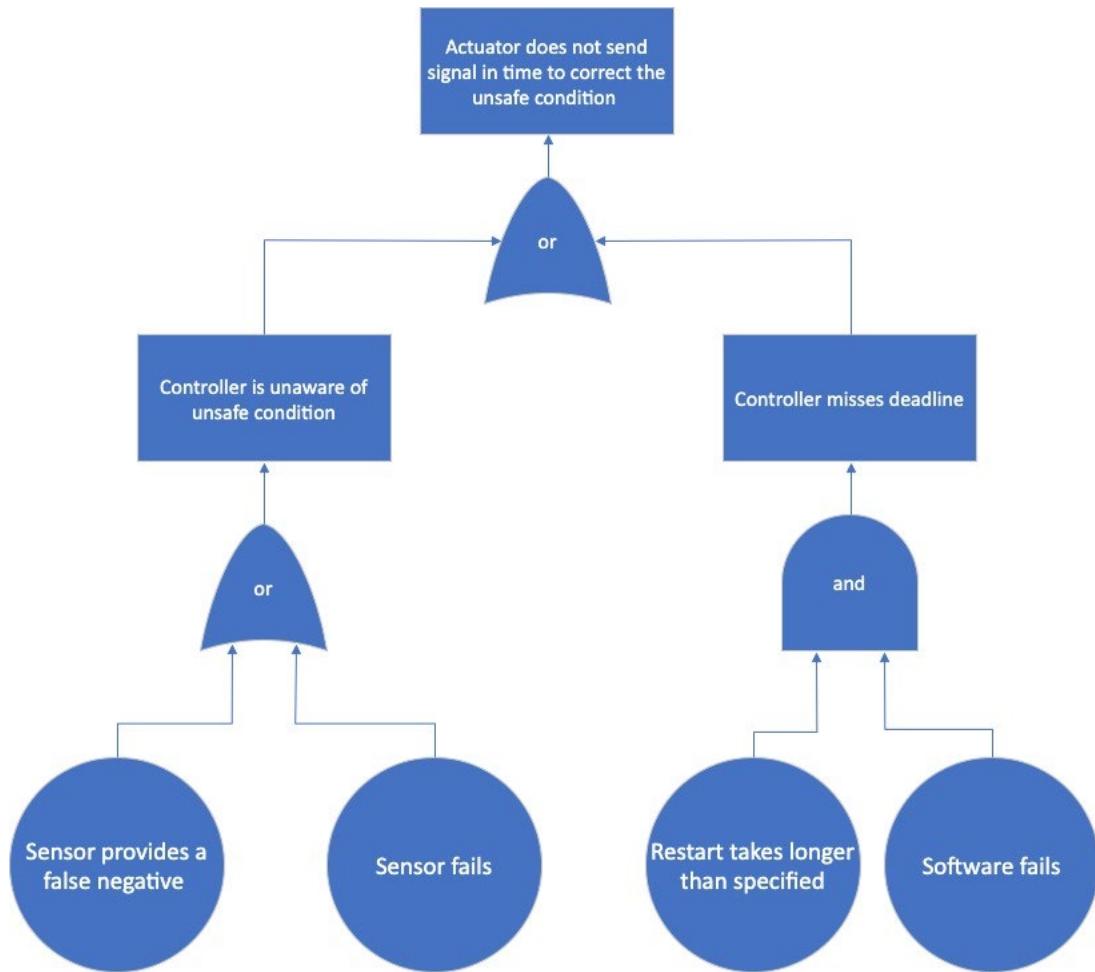

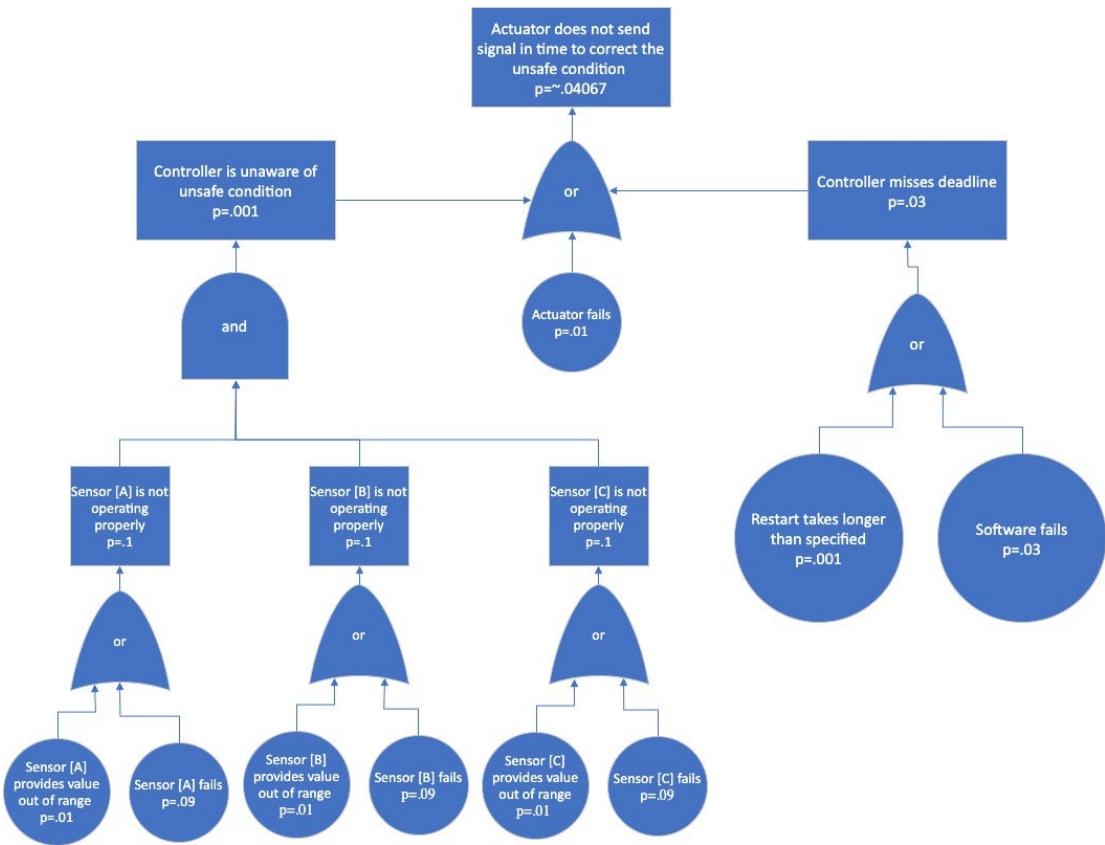

| Figure 9: Equivalent Fault Tree for a Group of Sensors (Employing a Redundancy Tactic) to Improve Robustness                        | 45 |

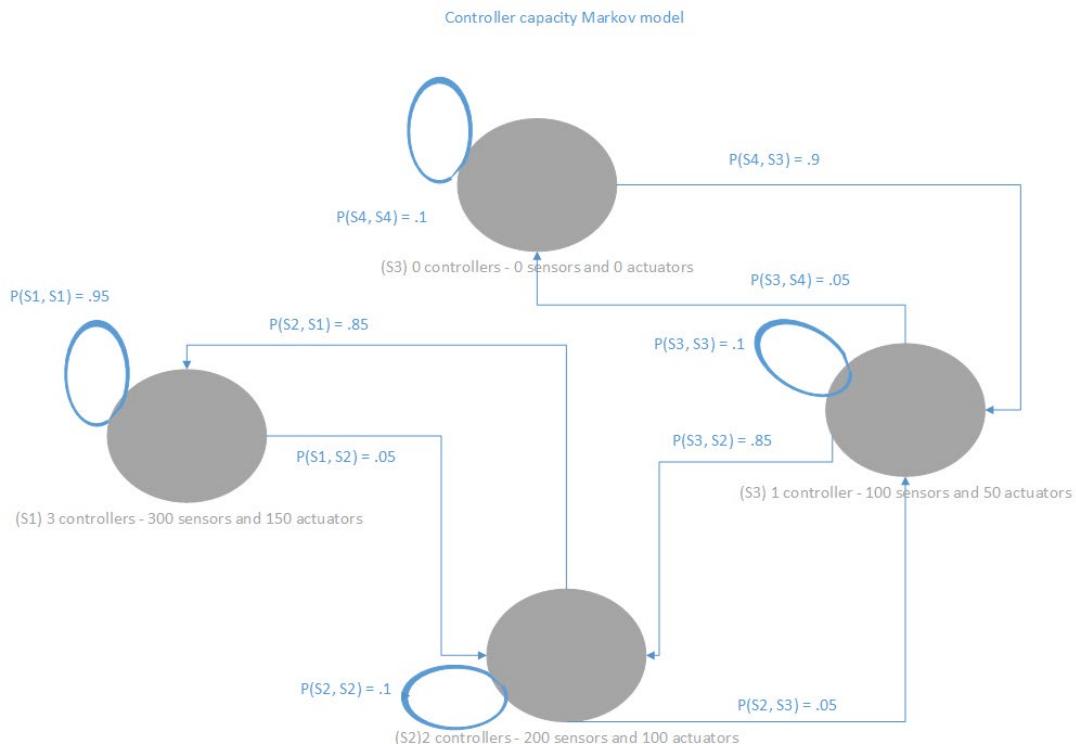

| Figure 10: Markov Model Representing the States That Correspond to System Capacity                                                  | 48 |

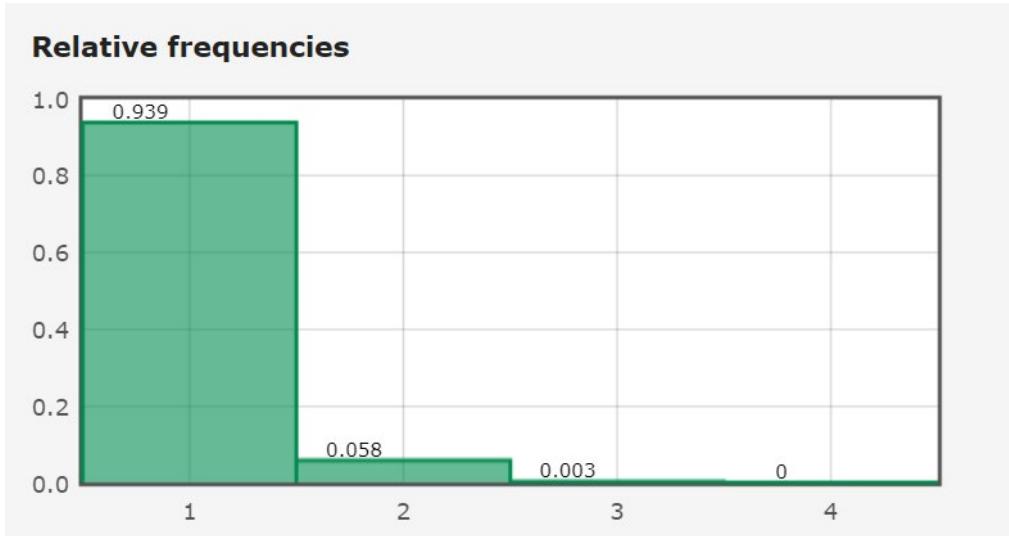

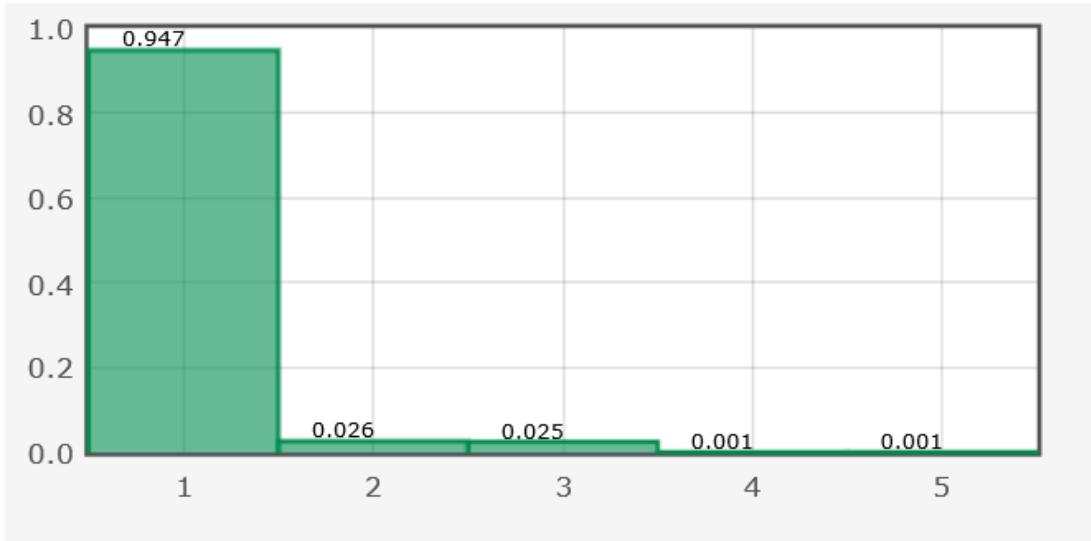

| Figure 11: Relative Frequencies Calculated for Each State in Our Markov Model from Our Initial Design                               | 49 |

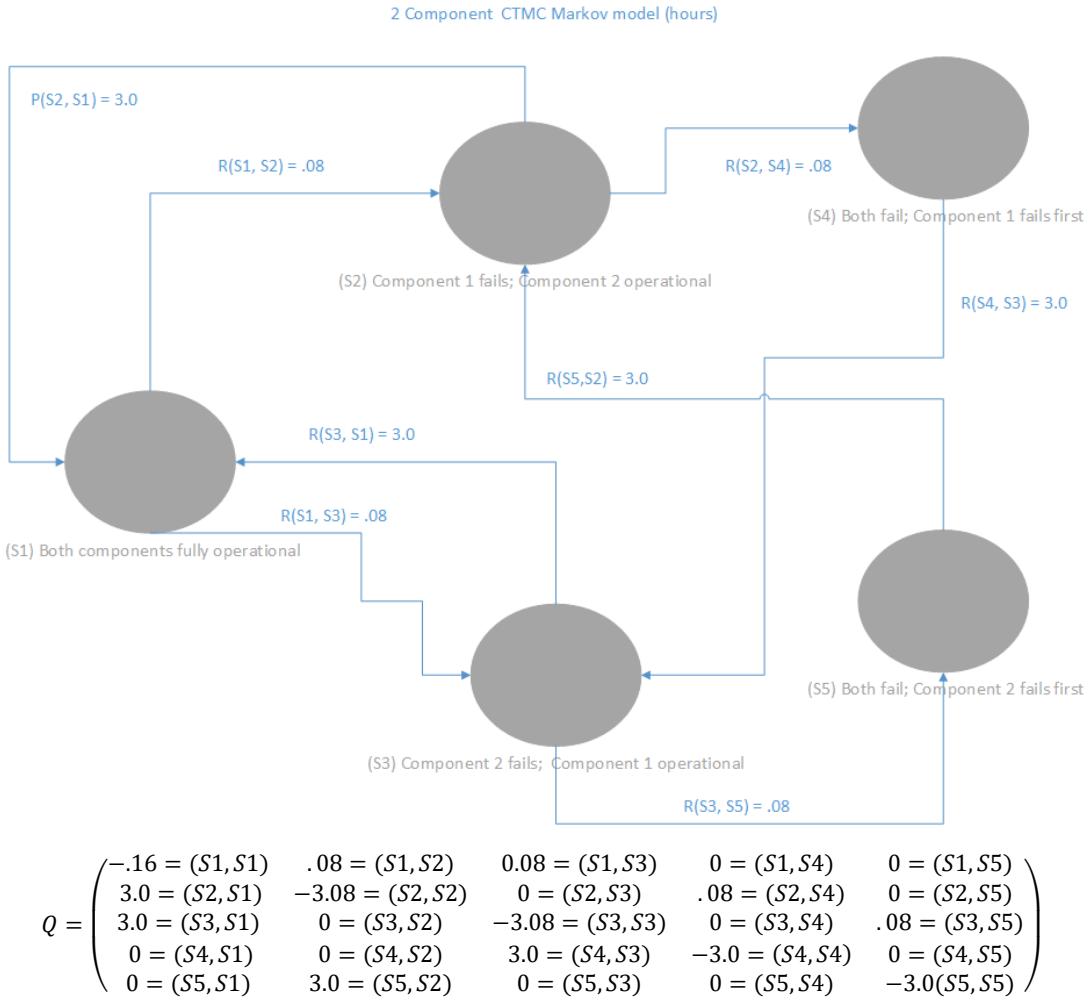

| Figure 12: CTMC State Transition Diagram and CTMC State Transition Matrix                                                           | 51 |

| Figure 13: Relative Frequencies Calculated for Each of the States in Our Markov Model from Our Initial Design                       | 52 |

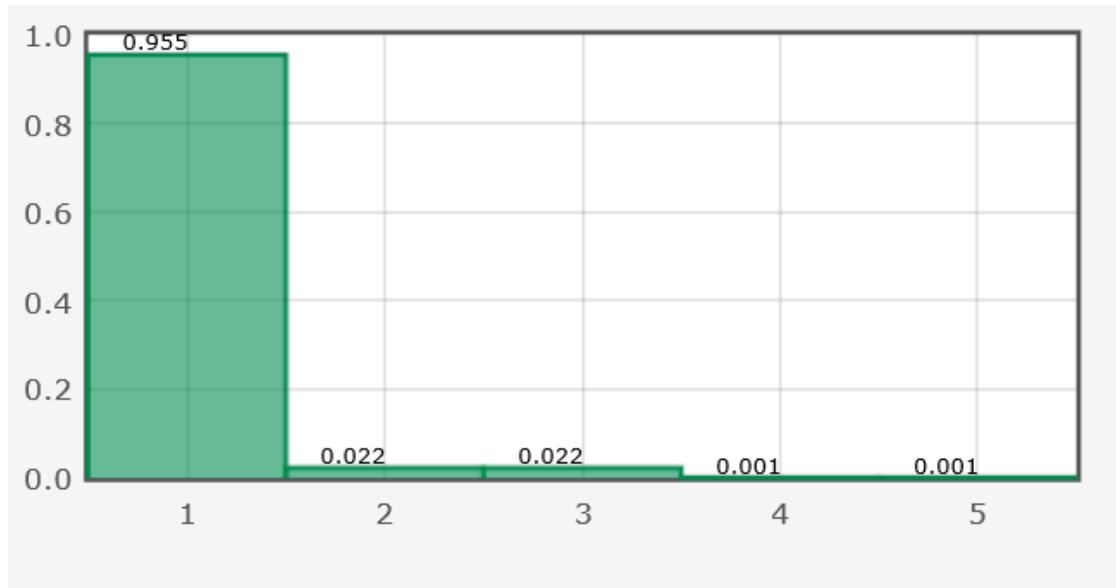

| Figure 14: CTMC State Transition Matrix for the Modified Design                                                                     | 53 |

| Figure 15: Relative Frequencies Calculated for Each of the States in Our Markov Model from Our New Design Reducing the Failure Rate | 53 |

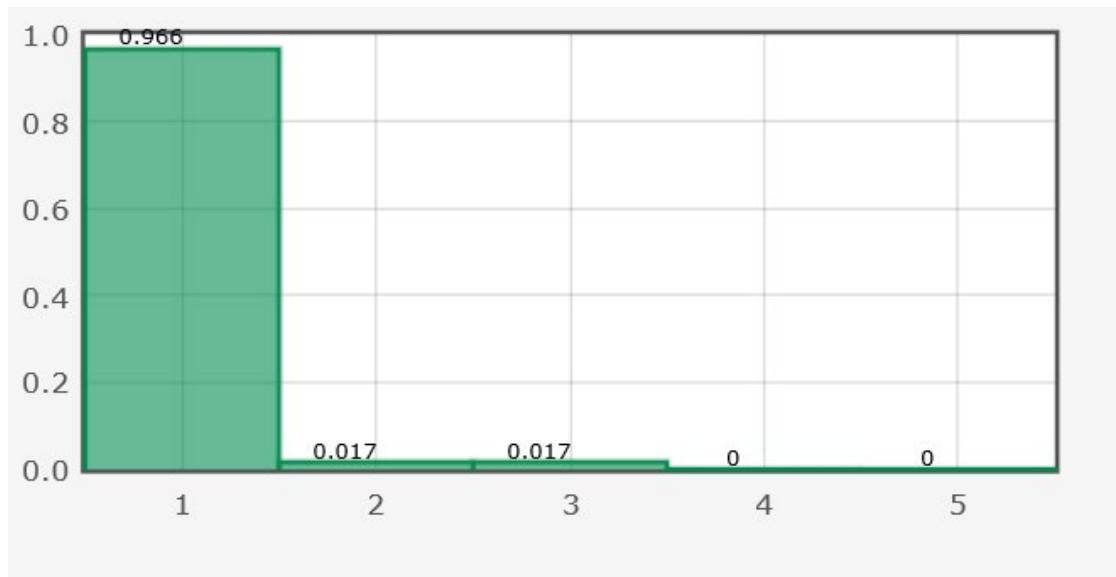

| Figure 16: CTMC State Transition Matrix for the Second Modification of the Design That Improves the Repair Rate                     | 54 |

| Figure 17: Relative Frequencies Calculated for Each of the States in Our Markov Model from Our New Design Improving the Repair Rate | 54 |

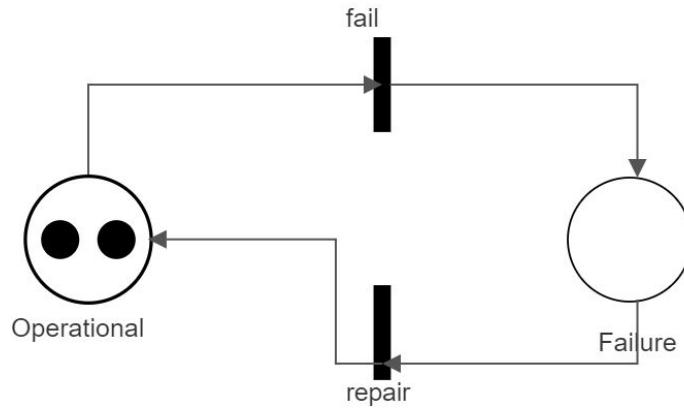

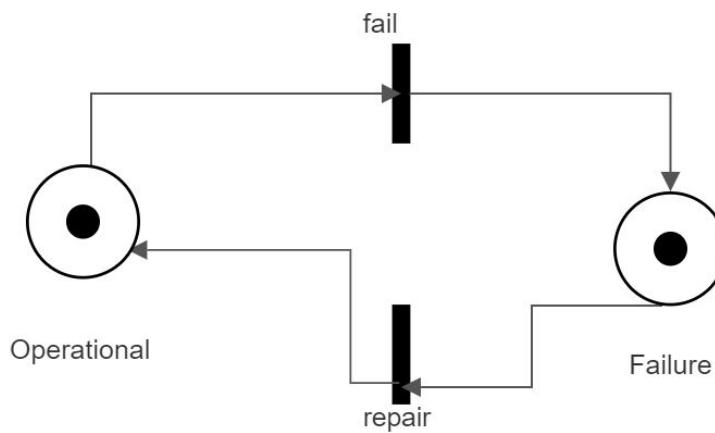

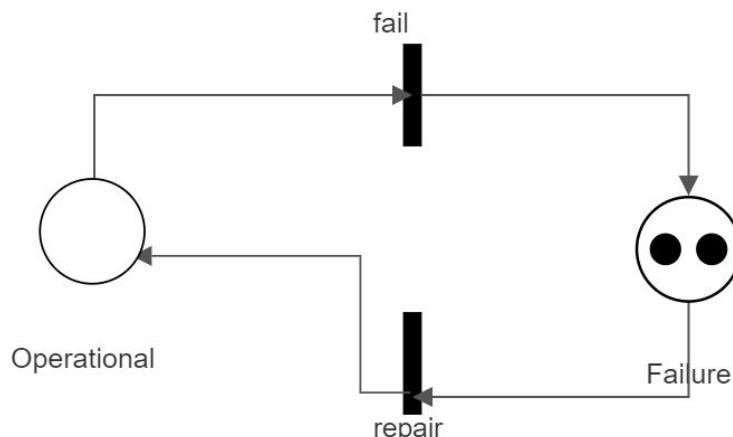

| Figure 18: Two Components, Both Operational                                                                                         | 57 |

| Figure 19: One Component Operational and One Failed                                                                                 | 57 |

| Figure 20: Two Components, Both Failed                                                                                              | 57 |

---

## List of Tables

|          |                                                                                                 |    |

|----------|-------------------------------------------------------------------------------------------------|----|

| Table 1: | Robustness Concerns, Questions, and Example Measures                                            | 7  |

| Table 2: | Robustness Tactics and Their Relationships to Architectural Approaches and Measures of Interest | 18 |

| Table 3: | Lifecycle Phases and Possible Analyses for Robustness                                           | 31 |

| Table 4: | Example Tactics-Based Robustness Questions                                                      | 32 |

| Table 5: | Robustness Modeling and Analysis Tools                                                          | 58 |

| Table 6: | Phases and Steps to Analyze an Architecture                                                     | 60 |

---

## Abstract

This report summarizes how to systematically analyze a software architecture with respect to a quality attribute requirement for robustness. The report introduces the quality attribute of robustness and common forms of robustness requirements for software architecture. It provides a set of definitions, foundational concepts, and a framework for reasoning about robustness and the satisfaction of robustness requirements by an architecture and by a system that realizes the architecture. It describes a set of architectural mechanisms—patterns and tactics—that are commonly used to satisfy robustness requirements. It also provides a set of steps that an analyst can use to determine whether an architecture documentation package provides enough information to support analysis and, if so, to determine whether the architectural decisions made contain serious risks relative to robustness requirements. An analyst can use these steps to determine whether those requirements, represented as a set of scenarios, have been sufficiently well specified to support the needs of analysis. The reasoning around this quality attribute should allow an analyst, armed with appropriate architectural documentation, to assess the robustness risks inherent in today's architectural decisions, in light of tomorrow's anticipated needs.

---

## 1 Goals of This Document

This document serves several purposes. It is

- an introduction to the quality attribute of robustness and common forms of robustness requirements

- a description of a set of mechanisms—patterns and tactics—that are commonly used to satisfy robustness requirements

- a means for an analyst to determine whether an architecture documentation package provides enough information to support analysis and, if so, to determine whether the architectural decisions made contain serious risks relative to robustness requirements

- a means for an analyst to determine whether those robustness requirements, represented as a set of scenarios, have been sufficiently well specified to support the needs of analysis

This document is one in a series of documents that, collectively, represent our best understanding of how to systematically analyze an architecture with respect to a set of well-specified quality attribute requirements [Kazman 2020a, 2020b]. The purpose of this document, as with all the documents in this series, is to provide a workable set of definitions, core concepts, and a framework for reasoning about quality attribute requirements and their satisfaction (or not) by an architecture and, eventually, a system. In this case, the quality attribute under scrutiny is *robustness*. The reasoning around this quality should allow an analyst, armed with appropriate architectural documentation, to assess the risks inherent in today’s architectural decisions in light of tomorrow’s anticipated tasks.

There are several commonly used and documented views of software and system architectures [Clements 2010]. The Comprehensive Architecture Strategy, for example, proposes four levels of architecture, each of which may be documented in terms of one or more views [Padilla 2019]:

1. functional architecture: The Functional Architecture provides a method to document the functions or capabilities in a domain by what they do, the data they require or produce, and the behavior of the data needed to perform the function.

2. hardware architecture: A Hardware Architecture specification describes the interconnection, interaction and relationship of computing hardware components to support specific business or technical objectives.

3. software architecture: A Software Architecture describes the relationship of software components, and the way they interact to achieve specific business or technical objectives.

4. data architecture: A Data Architecture provides the language and tools necessary to create, edit, and verify Data Models. A Data Model captures the semantic content of the information exchanged.

The focus of this document is almost entirely on the *software* architecture because a software architecture is the major carrier of and enabler of a system’s driving quality attributes. And since software typically changes much more frequently than hardware, it is often the focus of maintenance effort. There will, however, be implications of architectural decisions made on each of the other views.

In addition, other important decisions within a project will impact robustness—or any other quality attribute, for that matter. Even the best architecture will not ensure success if a project’s governance is not well thought out and disciplined; if the developers are not properly trained; if quality assurance is not well executed; and if policies, procedures, and methods are not followed. Thus, we do not see architecture as a panacea but rather as a necessary precondition to success, and one that depends on many other aspects of a project being well executed.

As we will show, there is not one single way to analyze for robustness. One can (and should) analyze for robustness at different points in the software development lifecycle, and at each stage in the lifecycle this analysis will take different forms and produce results accompanied by varying levels of confidence. For example, if there are documented architecture views but no implementation, the analysis will be less detailed and there will be less confidence in the results than if there were an existing implementation that could be scrutinized, tested, and measured. We will return to this issue of types of analysis and confidence in their outputs several times in this document.

---

## 2 On Robustness

Robustness has traditionally been thought of as the ability of a software-intensive system to keep working, consistent with its specifications, despite the presence of internal failures, faulty inputs, or external stresses, over a long period of time. Robustness, along with other quality attributes such as security and safety, is a key contributor to our trust that a system will perform today and tomorrow in a reliable manner. In addition, the notion of robustness has more recently come to encompass a system’s ability to withstand changes in its stimuli and environment without compromising its essential structure and characteristics. In this latter notion of robustness, systems should be malleable, not brittle, with respect to changes in their stimuli or environments. As such it is a highly important quality attribute to design into a system from the start, as it is unlikely that any nontrivial system could achieve this quality without conscientious and deliberate engineering. This is why we are interested in understanding robustness and how it is supported by appropriate architectural decisions.

This report begins with a survey of definitions for robustness. We introduce a set of *quality attribute scenarios*, including a *general scenario*, to define robustness requirements more precisely. This is followed by a discussion of the mechanisms that can be employed in a software architecture to promote robustness. And we conclude with a discussion of the various ways that an analyst can analyze for robustness, focusing on analysis checklists and analysis models and methods.

We create definitions for software and system quality attributes, like robustness, so that we can label and categorize quality requirements. These labels are then used by several groups during the development phase. Stakeholders and requirements engineers use the labels during requirements elicitation to create checklists, to assess coverage and completeness, and to collect similar requirements. This group is often concerned with *why* the software must be robust.<sup>1</sup> A second group using the quality attribute labels is architects, who use the labels to identify the relevant parts of the design body of knowledge to help them choose and instantiate mechanisms that promote the desired quality and satisfy the requirement. Finally, analysts and evaluators use the labels to choose methods to apply to validate and verify that the requirement is achieved. These latter groups are usually less concerned with the *why* of the requirement and more concerned with the scope and impact of what must be robust and constraints on how the robustness will be achieved. Also, these groups need enough precision in the requirement definition that it is actionable and verifiable.<sup>2</sup>

How can we define robustness? As with many notions in software, we take inspiration and guidance from more traditional areas of engineering. In civil engineering, for example, “robustness is taken to imply tolerance to damage from extreme loads or accidental loads, although the framework here is applicable to other adverse effects such as sensitivity to human error and deterioration” [Baker 2008].

---

<sup>1</sup> More formally, they are concerned that a requirement is *necessary* and *appropriate* [BKCASE 2018, Table 3].

<sup>2</sup> More formally, they are concerned that the requirements are *unambiguous*, *complete*, and *verifiable* [BKCASE 2018, Table 3].

But robustness is certainly an important quality of software systems. Gerald Jay Sussman, in his essay “Building Robust Systems: An Essay,” defines robust systems as “systems that have acceptable behavior over a larger class of situations than was anticipated by their designers” [Sussman 2007]. He goes on to say that “the most robust systems are evolvable: they can be easily adapted to new situations with only minor modification.” Finally, and perhaps most troubling considering the subject of this report, he notes that “common practice of computer science actively discourages the construction of robust systems.” This is because

*[i]n software engineering we are taught that the “correctness” of software is paramount, and that correctness is to be achieved by establishing formal specification of components and systems of components and by providing proofs that the specifications of a combination of components are met by the specifications of the components and the pattern by which they are combined. I assert that this discipline enhances the brittleness of systems. In fact, to make truly robust systems we must discard such a tight discipline. [Sussman 2007]*

A literature survey reviewed approaches to software robustness [Shahrokn 2013], and this term (and related terms such as “dependability” [Avizienis 2001]) also appears in quality attribute taxonomies such as that of the International Organization for Standardization (ISO) [ISO/IEC 2011]. However, the definitions used in these taxonomies are somewhat broad and the terminology varies. While ISO 25010(E) does not define robustness, it does define reliability as the “degree to which a system, product or component performs specified functions under specified conditions for a specified period of time.” This concept is closely related to the following concepts:

- *maturity: degree to which a system, product or component meets needs for reliability under normal operation*

- *availability: degree to which a system, product or component is operational and accessible when required for use*

- *fault tolerance: degree to which a system, product or component operates as intended despite the presence of hardware or software faults*

- *recoverability: degree to which, in the event of an interruption or a failure, a product or system can recover the data directly affected and re-establish the desired state of the system [ISO/IEC 2011]*

Similarly, the SWEBOK (*Guide to the Software Engineering Body of Knowledge*) [SWEBO 2014] does not mention robustness at all, but it does mention several related terms such as reliability and fault tolerance. Avizienis and colleagues define robustness as “dependability with respect to erroneous input” [Avizienis 2001].

Synthesizing these definitions, we can make some statements about robustness as a quality attribute. A system is “robust” if it

1. has acceptable behavior in normal operating conditions over its lifetime

2. has acceptable behavior in stressful environmental conditions (e.g., spikes in load)

3. can recover from or adapt to states that are outside its proper operating specification

4. can evolve and adapt to changes in its environment and stimuli with only minor changes

The fourth point deserves some elaboration. Ideally a robust system can handle changes in its environment and stimuli that we cannot anticipate. If a system needs to be easily extended—such as

to accommodate new data sources, new data types, and new sensors—then it can be said to be robust with respect to those stimuli. If a system scales linearly with spikes in demand with little effect on latency or throughput, then it can be said to be robust with respect to those spikes. If a system can accommodate changes in its environment—perhaps a platform upgrade—with relatively little expenditure of time and effort, and with few new bugs generated, it can be said to be robust with respect to that kind of maintenance stimulus. But each of these kinds of robustness involves other quality attributes—extensibility, performance, and maintainability. Robustness, viewed in this expansive way, potentially cuts across *all* quality attributes and is really the system’s ability to respond appropriately in the face of changing requirements and environments. Thus, this notion of robustness is not localized to a single quality attribute. While these notions of robustness are clearly important, they are not the focus of this report.

Finally, while the definitions of robustness provided above are helpful and provide context and scope for a robustness requirement, they do not have any criteria for satisfaction. For example, while the definitions suggest that it is important to *measure* robustness, they do not specify any specific measures. How can we say that one architecture is more robust than another? How can we say that an architecture is sufficiently robust? Further, the definitions do not distinguish among robustness challenges. For any system, some operating conditions will be easy to deal with, while others will be more difficult. Thus, these definitions allow us to talk about robustness in general, but to specify requirements for robustness we need a more precise definition.

In the field of software quality attributes, we can use *quality attribute scenarios* to create operational definitions. The next section defines quality attribute scenarios for the quality attribute of robustness.

---

### 3 Evaluating the Robustness of an Architecture

While we can precisely evaluate the robustness of an existing *implementation* of an architecture—by examining its bugs, faults, and failure history—we do not have this historical record when evaluating new architectures. Thus, we must analyze and evaluate new architectures in terms of their discernable characteristics. We use concrete scenarios to guide this analysis.<sup>3</sup>

We cannot precisely evaluate the robustness of an architecture any more than we can evaluate its performance, availability, or integrability. All quality attribute names are categories, and categories are too imprecise to be used for evaluation. Thus, we are better served by speaking of and measuring the robustness of an architecture, or a major subsystem, with respect to a set of anticipated and unanticipated faults or failures. And we specify these as scenarios. We will define a set of robustness scenarios in Section 4 as examples of the kinds of faults or failures that a system might be subjected to, and we will use these scenarios in our architecture analysis playbook (in Section 7).

To understand what it means to measure the robustness of a system, we need to understand the things that are involved in detection and recovery from faults and failures. To this end, we have surveyed the techniques that the software engineering research literature has proposed for robustness.

It is important to reiterate that while we restrict our attention in this section to analyzing *architectural* information for robustness, historically robustness analyses have focused on richer sets of information derived from a project’s logging, health monitoring, error handling, and history. The advantage of these richer sets of information is that we can potentially create more precise analyses. The disadvantage is that, to acquire such rich information, we need to build, deploy, and actually observe the system. At that point it can be very expensive and time consuming to mitigate problems relating to robustness. Thus, our objective in analyzing an *architecture* for robustness is to find a sweet spot wherein we can gain insight into the potential robustness characteristics of a system before much, if any, code has been committed.

#### 3.1 Measuring Robustness

When considering the robustness of a system, we must consider not only how resistant it is to failure but also the support that it provides to detect and recover from failures. Thus, we typically consider several system-level measures of robustness such as

- mean time between failures (MTBF) – a prediction, based on historical data, of how much time can be expected to elapse between system failures

- mean time to repair (MTTR)/estimated time of repair (ETR) – the time from a failure to when the system is once again operating according to its service-level agreement

---

<sup>3</sup> In this report we primarily focus on the aspects of robustness dealing with failures. For the aspects of robustness dealing with future changes, see the sidebars on “Designing for Unknown Unknowns” and “Architecting for the Unknown with Growth and Exploratory Scenarios” in Section 4, as well as the sidebar on “Assessing Brittleness” in Section 7. In addition, this topic is addressed in our technical report *Maintainability* [Kazman 2020b].

- availability/uptime percentage (the “nines”) – a measure of the orders of magnitude of a system’s predicted uptime

But these measures only give insight into the overall behavior of the system, from a robustness perspective. We can refine such measures into a more detailed set of questions about a system’s architecture. Consideration of such questions and their measures, and analysis of the architectural decisions that led to those measures, can lead to improved architectures.

A set of architectural robustness concerns, the questions related to those concerns, and potential measures that shed light on each of these questions are summarized in Table 1.

*Table 1: Robustness Concerns, Questions, and Example Measures*

| Concern                                                            | Supporting Questions                                                                                                                                                                                                                                                                                                                        | Example Measure                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prevention of faults or failures                                   | How many components have critical operational thresholds defined and monitored?<br><br>Does the system provide predictive modeling for thresholds (e.g., resource utilization)?<br><br>Does the software use mature components that are known to be reliable?<br><br>Does the system use hardware components that are known to be reliable? | <ul style="list-style-type: none"> <li>• Software MTBF</li> <li>• Hardware MTBF</li> <li>• Number of false positives for predictive analysis</li> <li>• Number or percentage of faults masked by detecting when the system is close to failure threshold</li> </ul> |

|                                                                    | Does the system quarantine unanticipated requests or bad inputs?                                                                                                                                                                                                                                                                            | <ul style="list-style-type: none"> <li>• % of confirmed unanticipated requests and invalid inputs quarantined</li> </ul>                                                                                                                                            |

|                                                                    | Does the system support retry?                                                                                                                                                                                                                                                                                                              | <ul style="list-style-type: none"> <li>• Number of retries needed or allowed</li> <li>• Percentage of operations or requests that need retries</li> <li>• % of retries successful</li> </ul>                                                                        |

| Detection of faults, error conditions, unsafe operating conditions | How many critical components can be monitored?                                                                                                                                                                                                                                                                                              | <ul style="list-style-type: none"> <li>• % of system components that are monitored</li> <li>• % of components that support runtime diagnostics</li> </ul>                                                                                                           |

|                                                                    | How effective is the monitoring?                                                                                                                                                                                                                                                                                                            | <ul style="list-style-type: none"> <li>• % of system faults or failures that are detected</li> <li>• Time to detect fault or failure or mean time to discover (MTTD)</li> <li>• Number of false positives</li> </ul>                                                |

|                                                                    | How complete is the fault modeling (e.g., failure modes and effects analysis [FMEA])?                                                                                                                                                                                                                                                       | <ul style="list-style-type: none"> <li>• Number of fault types identified</li> <li>• Number of fault types with detection mechanism and recovery strategies defined</li> <li>• % of anticipated faults that have explicit error handling</li> </ul>                 |

|                                                                    | What confidence do you have in detection, self-test, or voting?                                                                                                                                                                                                                                                                             | <ul style="list-style-type: none"> <li>• % of tests that produce correct/incorrect results at runtime</li> </ul>                                                                                                                                                    |

| Recovery from faults                                               | How do you restart failed nodes?<br><br>Does the system support failover?<br><br>Does the system support rollback to safe states?                                                                                                                                                                                                           | <ul style="list-style-type: none"> <li>• MTTR</li> <li>• System uptime and downtime</li> <li>• Failover time</li> <li>• Failover success rate</li> </ul>                                                                                                            |

|                                                                    | Does the system support degraded modes?                                                                                                                                                                                                                                                                                                     | <ul style="list-style-type: none"> <li>• Time spent in degraded mode of operations</li> <li>• % of time spent in degraded modes</li> </ul>                                                                                                                          |

## 3.2 Reasoning About Robustness Properties

For a large, complex software-intensive system to be robust, its architecture will typically support a mix of capabilities to detect and recover from failures, and it will typically contain redundant (backup) resources that can be invoked in the case of a failure of a “live” resource. When evaluating an architecture with respect to robustness, we need to assess the design decisions in an architecture that lead to robustness. That is, we need to understand how well the architecture has been designed with sufficient resources to withstand failures of individual system elements. And we need to further understand how the architecture has been designed to monitor and manage these resources.

Thus, we need to gauge the degree to which the architecture supports the following strategies:

- management of system resources, which we categorize into two main approaches:<sup>4</sup>

- *capacity sparing*: providing more resources than what is strictly necessary to accomplish the system’s functions, where some of these resources act as spares to replace failed resources. There are three main approaches to achieve this:

- *hardware redundancy* – We would like to understand the degree to which portions of the hardware architecture are protected by some sort of backup or redundant capability.

- *software redundancy* – Similarly such redundant capabilities may be spare processes, threads, containers, virtual machines, and so forth that can be used in case of a failure of the active component. We would like to understand the degree to which and ease with which software components can be replaced.

- *analytic redundancy* – A special case of software or hardware redundancy worth calling out is analytic redundancy [Bodson 1994, Sha 1998], where a complex component is mirrored by a simpler one that provides reduced, but more robust, functionality. For example, manual steering is analytically redundant to power steering in automobiles. We seek to understand which system functions have analytic spares to protect them in case of failure.

- *capacity management*: what functions to allocate to which resources

- growth potential: ease of adding capacity

- ease of matching system resources to tasks (e.g., matching a task’s resources to a suitable execution environment) and the ease with which a task can be moved around (dynamically or statically)

- management of system state, which has two approaches [Binder 2000]:

- *state observability* – We would like to understand the degree to which it is possible to examine critical properties of the system’s state such as memory and storage usage, processor utilization, liveness of processes and processors, communication channel utilization, latency, and transaction volume. These properties need to be observed and monitored because when such properties attain or exceed threshold or critical values, this is an indicator of a potential or actual fault. Thus, we need to determine what state properties are visible and what we can infer from these properties.

---

<sup>4</sup> We conceive of *approaches* as generalizations of tactics, which we describe in Section 5.1.

- *state controllability* – Coupled with state observability is state controllability. Given that we are able to observe the state of the system, for the system to be truly robust we must also be able to control that state, for example, by restarting bad processes, clearing memory, switching from a primary processor to a backup processor, choosing a level of service for a component, and choosing which components are active and which ones are passive or standby. Thus, we need to determine what state properties are controllable and what kinds of control we can exert.

Different scenarios will of course emphasize these approaches to different degrees. For example, detecting that memory is nearly full and instituting garbage collection involves state observability (examining current memory usage) and state controllability (putting the process into the garbage collection mode). Consider another scenario involving detecting a database failure and replacing it with its hot spare (a “mirror”). This scenario relies on being able to observe that the primary database has failed and on being able to control system state—directing all database connections to its mirror (a redundant copy of the database).

Analyzing for robustness, then, is about examining the mix of mechanisms selected for a set of robustness scenarios and predicting the percentage of faults and failures that can be observed (detected), prevented, masked, and recovered from (potentially deploying spare capacity such as redundant resources) to achieve system uptime requirements.

Note that many of the measures of robustness in Table 1 cannot be estimated from architectural artifacts alone. Many of these measures can only be measured off of a built and deployed system. However, this does not mean that we can do no useful analysis of an architecture with respect to robustness. As we will show in our “Playbook” for architecture analysis in Section 7, even where a measure does not exist or cannot be reliably obtained, an architecture can still be examined for its *fitness for purpose* with respect to the questions and measures described in Table 1.

### 3.3 Operationalizing the Measurement of Robustness

Thus, when analyzing an architecture for robustness, we have some analysis tradeoffs to make. We can analyze with respect to a particular set of scenarios and obtain a reasonably precise understanding of the architecture’s accommodation of those scenarios. But that understanding is necessarily narrow—limited to just those scenarios that we have considered. Alternatively, we can analyze with respect to metrics and get a broad understanding of the architecture’s overall level of predicted robustness—as measured by the metrics—but this gives us no insight into the specific risks involved in responding to specific scenarios. Furthermore, scenario-based analyses and design-level measures (like the degree of replication of critical resources) can be used to gain insight into a design. This insight therefore can be achieved *before* committing to an implementation. But precisely because these are measuring artifacts—like design specifications—that are created earlier in a system’s lifetime, they may not accurately reflect the eventual state of the system. This more accurate level of knowledge can only be achieved by measuring the system in operation.

For this reason, we recommend doing both: evaluating with respect to scenarios to get a deep understanding of some *anticipated* forms of robustness threats and, later in the lifecycle, adding analyses using measures from a system model or from the system in operation to obtain a more precise understanding of the qualities that the architecture (or any major subsystem within the architecture) helps to realize.

---

## 4 Robustness Scenarios

As stated in the book *Software Architecture in Practice*, quality attribute names themselves are of little use, as they are vague and subject to interpretation. The antidote to this vagueness is to specify quality attribute requirements as scenarios [Bass 2012]. A quality attribute scenario is simply a brief description of how a system is required to respond to some stimulus. Quality attribute scenarios, different from use cases, are architectural test cases. That is, they provide insights into the qualities that the architecture supports and any risks associated with the fulfillment of these scenarios.

A quality attribute scenario provides an operational definition of a quality of a system. The use of scenarios to specify quality attribute requirements for software dates back at least to 1994 [Kazman 1994]. Published examples include scenarios to specify requirements for seven of the most commonly occurring quality attributes [Bellomo 2015]: availability, interoperability, modifiability, performance, security, usability, and testability [Bass 2012]. More recently we have seen characterizations of the qualities of scalability and consistency [Klein 2015], integrability [Kazman 2020a], and maintainability [Kazman 2020b].

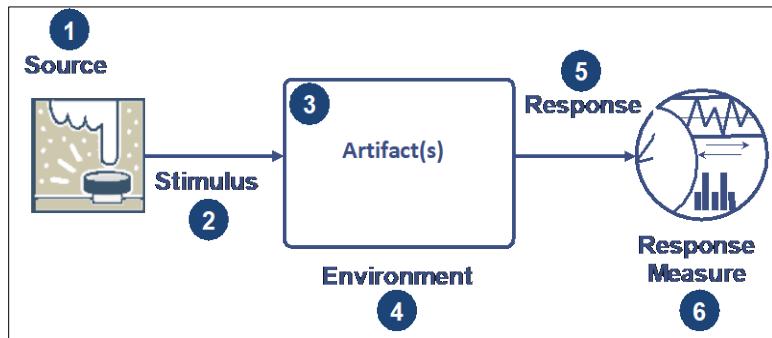

A quality attribute scenario has six parts [Bass 2012]. The two most important parts are a *stimulus* and a *response*. The stimulus is some event that arrives at the system, either during runtime execution (e.g., an invalid message arrives on a particular interface) or during development (e.g., a development iteration completes). The response defines how the system should behave when the stimulus occurs. For example, in response to an invalid message arriving, the system should log the event and send an error response message. In response to a development iteration completing, the unit and integration tests should be run and the test results reported.

The stimulus and response form the core of our operational definition by specifying the operation that we will measure. The third part of a scenario, the *response measure*, defines how we will measure the response and the satisfaction criteria. The response measure includes a metric and a threshold.

The other three parts of the scenario provide more details. We specify the *source* of the stimulus, to provide context for the scenario. We also specify the *environment*, which is the conditions under which the stimulus occurs and the response is measured. Finally, we specify the *artifact*, which is the portion of the system to which the requirement applies. Often, the artifact is the entire system, but in the example above, we might treat invalid messages on external interfaces differently from invalid messages on internal interfaces.

During requirements elicitation, we may specify the parts of a scenario in any order. We often begin with stimulus and response, although environment, source, or artifact may be the initial trigger for the requirement. In any case, once the scenario is specified, we usually arrange the parts to tell a story, as shown in Figure 1.

Figure 1: The Form of a General Scenario

In this way, the quality of the architecture, including measures that reflect on its robustness, can be continuously tracked and assessed. And if changes are made that undermine some architectural characteristic, the test case fails and appropriate remedial action can be taken.

### Sidebar: Scenarios as Architectural Test Cases

In architecture analysis, scenarios are “architectural test cases.” We use them to determine whether the architecture—as envisioned or as created—is consistent with its specification. Before the system is built, we use scenarios to assess the quality of the architectural decisions. Once the system exists, we can continue to use scenarios to assess the quality of the architecture as it evolves.

For runtime quality attributes, scenarios may become much more than simply guides for analysts. They can be used as acceptance tests and made part of the regression test suite. Or they can even be manifested as system health measures that are logged or monitored continuously at runtime. If the checks are at runtime, checking can be built into a system monitor; if the checks are run at build time, checking can be built into a continuous integration pipeline. In either case, checking requires appropriate visibility into system response measures (e.g., the ability to track latency, resource usage, and mean time to failure [MTTF]). For non-runtime quality attributes (assuming that source code is available), we can monitor the quality or degradation of the architecture’s modular structure via architecture analysis tools, or we can monitor project management measures of the effort required to make changes.

## 4.1 General Scenario for Robustness

As we noted in the previous section, operational definitions are not exclusive: There is not a single scenario that specifies all the possible measurements that could characterize a quality like robustness. However, if we look at the definitions of robustness, we find some common themes. A *general scenario* maps those common themes into the parts of a quality attribute scenario, providing a template that we can use to create *concrete scenarios* for a particular system. The general scenario defines the *type* of the values for each part of the scenario, and a concrete scenario for robustness of a system is created by specifying one or more system-specific values of the selected type for each part of the scenario. (We say values—plural—because, for example, a scenario might have more than one response measure.)

Here is the general scenario for robustness:<sup>5</sup>

| Scenario Part    | Possible Type for Each Value                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Source           | Software, external system, or hardware                                                                                                                                                                                                                                                                                                                                                       |

| Stimulus         | <p>One of the following:</p> <ul style="list-style-type: none"> <li>• Software fault or failure</li> <li>• Hardware failure</li> <li>• Unanticipated message</li> <li>• Spike in demand</li> <li>• Invalid input</li> <li>• Diagnostic test fails</li> <li>• Unresponsive component</li> <li>• Responds after deadline</li> <li>• Defined threshold (e.g., processor utilization)</li> </ul> |

| Artifact         | <p>One of the following:</p> <ul style="list-style-type: none"> <li>• Single software element</li> <li>• Multiple software elements</li> <li>• Hardware element</li> <li>• Entire software system</li> </ul>                                                                                                                                                                                 |

| Environment      | <p>One of the following:</p> <ul style="list-style-type: none"> <li>• Normal operations</li> <li>• Degraded modes</li> </ul>                                                                                                                                                                                                                                                                 |

| Response         | <p>One or more of the following:</p> <ul style="list-style-type: none"> <li>• Fault detected and administrators notified</li> <li>• System operates in degraded mode</li> <li>• Fault detected, logged, and reported</li> <li>• Fault repaired</li> <li>• Fault prevented, logged, and reported</li> <li>• Diagnostics completed</li> </ul>                                                  |

| Response Measure | <p>One or more of the following:</p> <ul style="list-style-type: none"> <li>• MTTD</li> <li>• MTTR</li> <li>• Percentage uptime</li> <li>• Failover time</li> <li>• Uptime</li> <li>• % messages delivered</li> <li>• % of responses received</li> </ul>                                                                                                                                     |

## 4.2 Example Scenarios for Robustness

Each of the following example scenarios is constructed by selecting one or more of the types of values from each of the six parts of the general scenario and specifying a system-specific value. For each example, we will use an easy-to-understand “typical” system. In practice, you would choose values that are as precise as possible, in the context of your system. In each example, notes

---

<sup>5</sup> This general scenario is adapted from Bass and colleague's general scenario for modifiability [Bass 2012, §7.1].

in square brackets are added to trace back to general scenario types in cases where the traceability is not obvious.

### **Sidebar: Architecting for the Unknown with Growth and Exploratory Scenarios**

As we will discuss in Section 5, a great challenge of building robust systems is architecting for the unknown. Since we cannot enumerate all possible future changes or failure conditions, we cannot create architectural responses to all unknowns. And even if we could, the time to complete a project would grow enormously, and the cost/benefit ratio of architecting for less and less likely failures and changes would shrink to vanishingly small. So what is the prudent architect or analyst to do?

We advocate employing growth and exploratory scenarios as a means of exploring the space of conditions that we want to explicitly consider in our architecture design and analysis process. Growth scenarios represent anticipated growth and anticipated stresses on a system. For example, if we know based on our history that we are likely to add sensors to the system on a regular basis, we can create a growth scenario that captures this anticipated future change in requirements.

Exploratory scenarios are ideally used to ask “what if” questions, to help probe our understanding of more extreme potential changes and more extreme environmental conditions. What would happen if all our processors failed simultaneously? How much work would be required to change the architecture to manage tighter coordination among system instances? What would happen if our backup network failed shortly after our main network failed? What would happen if we needed to report updates every second instead of reporting them hourly? What would happen under conditions of extreme heat, extreme load, or extreme growth in user requests? These kinds of scenarios, while perhaps unlikely, help us understand the limits of our architecture and the tradeoffs that have been made. They can also be used with respect to any quality attribute, such as in evaluating the robustness of an architecture to future security or maintainability requirements. As such they are a crucial tool in the toolbox of the designer and the analyst.

Collectively, growth and exploratory scenarios allow architects or analysts to explore the robustness of an architecture with respect to future changes or failure conditions that fall outside of current requirements but are perhaps more likely than not to become future requirements. Growth and exploratory scenarios aren’t a panacea for the unknown though, as they still require someone to think of potential changes or failure conditions prior to making architectural decisions or evaluating an architecture.

#### 4.2.1 Scenario 1: System Initialization Times Out

This example scenario describes how failure can be detected and recovered from, for system initialization of a networked avionics system such as a navigation system.

| Scenario Part    | Value                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------|

| Source           | Navigation System initialization configuration file errors                                        |

| Stimulus         | Navigation System initialization times out.                                                       |

| Artifact         | Navigation System initialization component                                                        |

| Environment      | Normal operations                                                                                 |

| Response         | The timeout is detected, and the system is initialized using a standard configuration.            |

| Response Measure | Timeout is detected 100% percent of the time.<br>System initialization is restarted within 10 ms. |

Note that in this scenario—as in many scenarios—multiple response measures are specified. Furthermore, in some cases, multiple scenarios are needed to completely specify the quality attribute requirement. For instance, the environment in the example scenario above was normal operations, and one of the responses was to reinitialize using a standard configuration. Another scenario, with identical stimulus and response measures, might specify an environment of the system being restarted in a degraded mode, and the response measure for restarting the system initialization could be changed to 20 ms.

#### 4.2.2 Scenario 2: Software Fault and Recovery

This example scenario describes the robustness of the Flight Management System to recover from the failure of a software element.

| Scenario Part    | Value                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Source           | RADAR Altimeter Manager                                                                                                           |

| Stimulus         | RADAR Altimeter Manager does not report sensor data by deadline.                                                                  |

| Artifact         | Flight Management System                                                                                                          |

| Environment      | Normal operation                                                                                                                  |

| Response         | Restart RADAR Altimeter Manager.<br>Detect fault.<br>Log error.<br>Failover to backup.                                            |

| Response Measure | Detect fault within 2 ms.<br>Restart within 10 ms.<br>Switch to backup in 5 ms.<br>Altimeter data is available 100% of operation. |

#### 4.2.3 Scenario 3: Resource Threshold Is Approached

This example scenario describes how the system responds when a critical system resource is near its capacity.

| Scenario Part    | Value                                                                                 |

|------------------|---------------------------------------------------------------------------------------|

| Source           | Processor Monitor                                                                     |

| Stimulus         | Total CPU utilization is at 85%.                                                      |

| Artifact         | Flight Management System                                                              |

| Environment      | Normal operation                                                                      |

| Response         | Disable noncritical functions or message throttling.<br>Detect fault.<br>Log error.   |

| Response Measure | Detect fault within 2 ms.<br>Restart within 10 ms.<br>All critical deadlines are met. |

#### 4.2.4 Scenario 4: Hardware Failure and Restart

This example scenario describes how the system responds when a critical system resource fails.

| Scenario Part    | Value                                                                                 |

|------------------|---------------------------------------------------------------------------------------|

| Source           | Processor Monitor                                                                     |

| Stimulus         | CPU overheats and shuts down.                                                         |

| Artifact         | Flight Management System                                                              |

| Environment      | Normal operation                                                                      |

| Response         | Failover to other CPUs (hot spare).<br>Detect fault.<br>Log error.                    |

| Response Measure | Detect fault within 2 ms.<br>Restart within 10 ms.<br>All critical deadlines are met. |

---

## 5 Mechanisms for Achieving Robustness

We have thus far focused most of our attention on analyzing an architecture for robustness. But analysis and design are two sides of the same coin. Now we turn our attention to the architectural design task of *achieving* robustness.

An architect must choose a set of design concepts to construct a solution for any quality attribute requirement [Cervantes 2016], and the architecture that the analyst is given to examine will contain design decisions regarding such concepts. Here we generically refer to these design concepts as “mechanisms.” We will discuss and provide examples of two important kinds of architectural design mechanisms: *tactics* and *patterns*. These mechanisms are the architect’s main tools to achieve a desired set of robustness characteristics.

### 5.1 Tactics

A mechanism is an architectural approach that we can take to control a quality attribute. Many discussions of mechanisms—for example, Bass and colleagues [Bass 2012]—focus on *technical mechanisms*, such as architectural patterns and tactics. Technical mechanisms are sufficient to satisfy requirements for quality attributes such as availability or consistency in a big data system. For other quality attributes such as security and robustness, technical mechanisms are necessary but not sufficient to satisfy some system-level requirements, and the technical mechanisms must be accompanied by *governance mechanisms*. For example, security defense-in-depth might begin with physical security, which requires governance to enforce access procedures. For robustness, any modification to the software will be extremely difficult without governance such as acquisition practices that ensure that appropriate architecture, design, and code documentation are produced, that code reviews are performed, that test suites are maintained, and that employees are appropriately trained so that they do not undermine the integrity of the architecture with the changes they implement.

Governance mechanisms related to robustness in the Department of Defense (DoD) context appear in discussions of the Modular Open System Approach (MOSA) [ODASD 2017] and DoD software acquisition practices [DIB 2019]. The rest of this section focuses on technical mechanisms for robustness: Architecture approaches are commonly employed to satisfy the types of scenarios that we outlined in the previous section.

In practice, the terminology used for technical mechanisms is informal, and often the term is used to refer to any decision made during the architecture design process or to any fragment of the architecture that is intended to address some particular functional or quality attribute-related concern. In this report, we will consider two specific types of mechanisms:

- **Architectural Patterns.** *Design patterns* are conceptual solutions to recurring design problems that exist in a defined context. A pattern is *architectural* when its use directly and substantially influences the satisfaction of an architecture driver such as a quality attribute scenario [Cervantes 2016]. An architectural pattern defines a set of element types and interactions; the topological layout of the elements; and constraints on topology, element behavior, and interactions [Bass 2012].

- Architectural Tactics. *Tactics* are smaller building blocks of design than architectural patterns, focused on a single element or interaction, in contrast to a pattern that defines a collection of elements [Bass 2012].

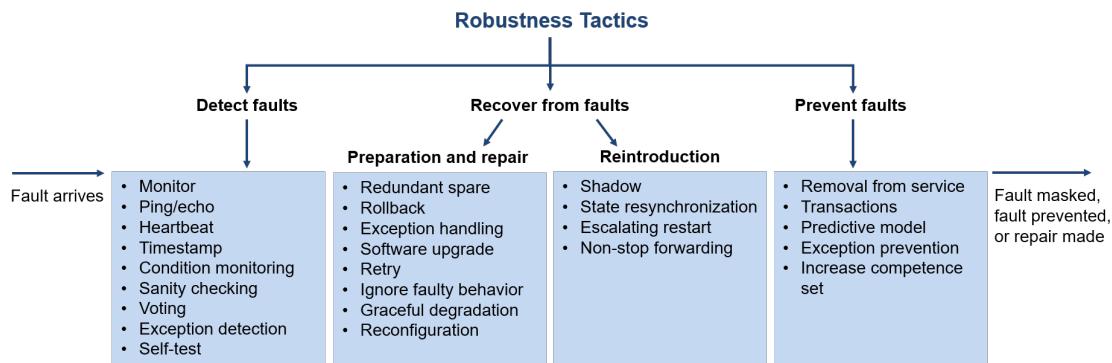

Since tactics are simpler and more fundamental than patterns, we begin our discussion of mechanisms for robustness with them. Tactics are the building blocks of design, the raw materials from which patterns, frameworks, and styles are constructed. Each set of tactics is grouped according to the quality attribute goal that it addresses. The goals for the robustness tactics shown in Figure 2 are to enable a system, in the face of a fault, to prevent, mask, or repair the fault so that a service being delivered by the system remains compliant with its specification. The tactic descriptions presented below are derived, in part, from the third edition of *Software Architecture in Practice* [Bass 2012]. We discuss each of the tactics presented in Figure 2 in more detail below. For each tactic that we discuss, we not only describe the tactic but also relate it to the measures described in Section 3.1 as a way of describing the intent and impact of the tactic.

Figure 2: Robustness Tactics

These tactics are known to influence the responses (and hence the costs) in the general scenario for robustness (e.g., number of components affected, effort, calendar time, new defects introduced). Table 2 summarizes the tactics presented in this section, and how each relates to the characteristics and measures presented in Sections 3.1 and Figure 2. The table assesses the relationships between the availability (robustness) tactics and the architectural approaches of capacity sparing, capacity management, state observability, and state controllability, each of which can contribute to achieving higher measures of MTTF and MTTR. An architect, in designing for high availability, needs to make decisions to

- provision spare capacity (including, in most cases, providing for backup resources)

- manage the capacity of the resources that are available

- observe the state of the system to determine when the system, or some part of it, is inconsistent with respect to its specification

- control the state of the system to keep the system alive and healthy, consistent with its specification

By consciously managing these system strategies and concerns, the architect can design to reduce the likelihood of a failure, thus increasing the MTTF measure, or to recover from failures more quickly, thus reducing the MTTR measure.

Table 2: Robustness Tactics and Their Relationships to Architectural Approaches and Measures of Interest

| Tactic                  | Architectural Approaches |                |               |                | Measures |      |

|-------------------------|--------------------------|----------------|---------------|----------------|----------|------|

|                         | Capacity Sparing         | Capacity Mgmt. | State Observ. | State Control. | MTTF     | MTTR |

| Monitor                 |                          |                | +             |                |          | +    |

| Ping/Echo               |                          |                | +             |                |          | +    |

| Heartbeat               |                          |                | +             |                |          | +    |

| Timestamp               |                          |                | +             |                |          | +    |

| Condition Monitoring    |                          |                | +             |                |          | +    |

| Sanity Checking         |                          |                | +             |                |          | +    |

| Voting                  |                          |                | +             |                |          | +    |

| Exception Detection     |                          |                | +             |                |          | +    |

| Self-test               |                          |                | +             |                |          | +    |

| Active Redundancy       | +                        |                |               |                | +        | +    |

| Passive Redundancy      | +                        |                |               |                | +        | +    |

| Spare                   | +                        |                |               |                |          | +    |

| Rollback                |                          |                |               | +              |          | +    |

| Exception Handling      |                          |                |               | +              |          | +    |

| Software Upgrade        |                          |                |               | +              |          | +    |

| Retry                   |                          |                |               | +              | +        | +    |

| Ignore Faulty Behavior  |                          |                |               | +              | *        | +    |

| Graceful Degradation    |                          | +              |               | +              | *        | *    |

| Reconfiguration         | +                        | +              |               | +              | *        | *    |

| Shadow                  |                          |                |               | +              |          | +    |

| State Resynchronization |                          |                |               | +              |          | +    |

| Escalating Restart      |                          |                |               | +              |          | +    |

| Non-stop Forwarding     |                          | +              |               | +              | *        | *    |

| Removal from Service    | +                        |                |               | +              | +        |      |

| Transactions            |                          |                |               | +              | +        | +    |

| Predictive Model        |                          |                | +             |                | +        |      |

| Tactic                  | Architectural Approaches |                |               |                | Measures |      |

|-------------------------|--------------------------|----------------|---------------|----------------|----------|------|

|                         | Capacity Sparing         | Capacity Mgmt. | State Observ. | State Control. | MTTF     | MTTR |

| Exception Prevention    |                          |                |               | +              | +        |      |

| Increase Competence Set |                          |                |               | +              | +        |      |

*Note: A plus sign indicates that the tactic positively addresses maintainability properties and hence measures, and an asterisk indicates that the tactic might positively or negatively address the measure, depending on its realization. A blank cell means that the property has no consistent effect on the measure.*

### Sidebar: Designing for Unknown Unknowns

Many of the robustness tactics are employed because we acknowledge that faults in *parts* of the system are a normal occurrence; hence we can architect to detect and recover from those faults, increasing the likelihood that faults do not become failures. But these tactics are primarily aimed at recovering from known, anticipated faults. Several of the robustness tactics presented below are, however, particularly helpful in considering how to deal with problems that we cannot anticipate—the so-called unknown unknowns. These tactics include *rollback*, *ignore faulty behavior*, *abort*, *analytic redundancy*, *masking*, and *return to safe state*.

Every architect must consider and balance cost, schedule, and risk when making design decisions. As such it is impossible to deal with *all* unknown unknowns. There is always an envelope of faults and error states that a prudent architect chooses to handle. The unknown unknowns are then the complement to these identified faults and states. One of the motivations for enumerating tactics is to help architects reflect on and, ideally, broaden that “known” envelope.

As an analyst, when you see a tactic such as *exception handling* being employed, you should ask which exceptional states that tactic handles and additionally ask what happens to exceptional states not captured. Models, such as fault tree analysis, can help analysts understand the scope of the tactics that architects are considering.

#### 5.1.1 Detect Faults

Before any system can take action regarding a fault, the presence of the fault must be detected or anticipated. Tactics in this category include the following:

- *Monitor*. A monitor is a component that is used to monitor the state of health of various other parts of the system: processors, processes, input/output, memory, and so forth. A system monitor can detect failure or congestion in the network or other shared resources, such as from a denial-of-service attack. It orchestrates software using other tactics in this category to detect malfunctioning components. For example, the system monitor can initiate *self-tests* or be the component that detects faulty *timestamps* or missed *heartbeats*.<sup>6</sup>

<sup>6</sup> When the detection mechanism is implemented using a counter or timer that is periodically reset, this specialization of *system monitor* is referred to as a *watchdog*. During nominal operation, the process being monitored will periodically reset the watchdog counter/timer as part of its signal that it's working correctly; this is sometimes referred to as “petting the watchdog.”

- *Ping/echo*. Ping/echo refers to an asynchronous request/response message pair exchanged between nodes, used to determine reachability and the round-trip delay through the associated network path. But the echo also determines that the pinged component is alive and responding correctly. The ping is often sent by a system monitor. Ping/echo requires a time threshold to be set; this threshold tells the pinging component how long to wait for the echo before considering the pinged to have failed (“timed out”). Standard implementations of *ping/echo* are available for nodes interconnected via the Internet Protocol (IP).

- *Heartbeat*. A heartbeat is a fault detection mechanism that employs a periodic message exchange between a system monitor and a process being monitored. A special case of heartbeat is when the process being monitored periodically resets the watchdog timer in its monitor to prevent it from expiring and thus signaling a fault. For systems where scalability is a concern, transport and processing overhead can be reduced by piggybacking heartbeat messages on to other control messages being exchanged between the process being monitored and the distributed system controller. The big difference between heartbeat and ping/echo is what holds the responsibility for initiating the health check—the monitor or the component itself.

- *Timestamp*. This tactic is used to detect incorrect sequences of events, primarily in distributed message-passing systems. A timestamp of an event can be established by assigning the state of a local clock to the event immediately after the event occurs. Simple sequence numbers can also be used for this purpose, if time information is not important.

- *Condition monitoring*. This tactic involves checking conditions in a process or device or validating assumptions made during the design. By monitoring conditions, this tactic prevents a system from producing faulty behavior. The computation of checksums is a common example of this tactic. However, the monitor must itself be simple (and, ideally, provable) to ensure that it does not introduce new software errors.

- *Sanity checking*. This tactic checks the validity or reasonableness of specific operations or outputs of a computation. This tactic is typically based on a knowledge of the internal design, the state of the system, or the nature of the information under scrutiny. It is most often employed at interfaces to examine a specific information flow.

- *Voting*. The most common realization of this tactic is referred to as Triple Modular Redundancy (or TMR, as we will discuss in Section 5.2.2), which employs three components that do the same thing, each of which receives identical inputs and forwards its output to voting logic, used to detect any inconsistency among the three output states. Faced with an inconsistency, the voter reports a fault. It must also decide what output to use. It can let the majority rule or choose some computed average of the disparate outputs. This tactic depends critically on the voting logic, which is usually realized as a simple, rigorously reviewed, and tested singleton so that the probability of error is low.

- *Replication* is the simplest form of *voting*; here, the components are exact clones of each other. Having multiple copies of identical components can be effective in protecting against random failures of hardware, but this approach cannot protect against design or implementation errors, in hardware or software, since there is no form of diversity embedded in this tactic.